複合電(diàn)極SLC單層芯片電(diàn)容的制備方法

發布者 : admin

發布時間 : 2022/04/26 09:04:46

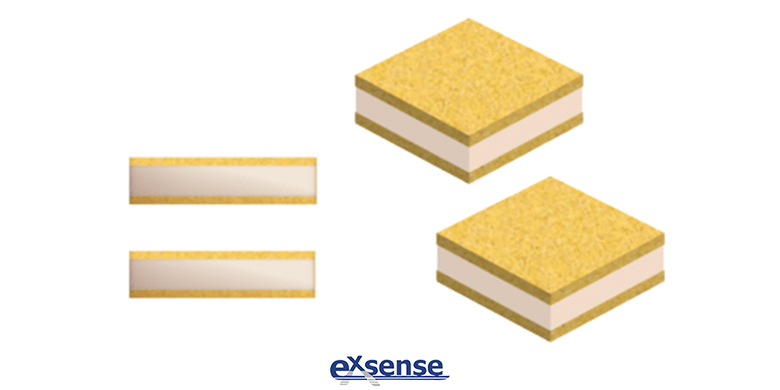

根據《複合電(diàn)極SLC單層芯片電(diàn)容》可(kě)知,複合電(diàn)極SLC單層芯片電(diàn)容的下表面電(diàn)極可(kě)以很(hěn)好地與錫膏回流焊或銀膏焊接,其中(zhōng)的钛鎢(TiW)層使銅(Cu)層與電(diàn)容陶瓷基片更好地結合,并具(jù)有(yǒu)阻擋作(zuò)用(yòng);銅層作(zuò)為(wèi)阻擋層,用(yòng)于阻擋外界對過渡層的破壞,并具(jù)有(yǒu)焊接作(zuò)用(yòng);金(Au)層既是焊接層,也是保護層,有(yǒu)效地阻擋了錫膏回流焊時焊錫滲透至銀層中(zhōng),使用(yòng)錫膏回流焊的焊接效果良好,不會存在錫銀合金現象或銀遷移現象。而且,錫膏回流焊溫度為(wèi)260℃,而複合電(diàn)極SLC單層芯片電(diàn)容中(zhōng)下表面電(diàn)極的金層與錫膏回流焊不會導緻銀遷移現象,所以其耐溫溫度可(kě)達到260℃。若采用(yòng)高溫錫,耐溫溫度可(kě)達300℃以上。另外,複合電(diàn)極SLC單層芯片電(diàn)容中(zhōng)上表面電(diàn)極的銀層表面能(néng)與鋁線(xiàn)、銅線(xiàn)或金線(xiàn)很(hěn)好地邦定焊接,邦定打線(xiàn)後不脫線(xiàn),可(kě)靠性高。而複合電(diàn)極SLC單層芯片電(diàn)容的制備方法如下:

一、在片狀電(diàn)容陶瓷基材的一表面上印刷銀漿,然後進行高溫燒結。

①将電(diàn)容陶瓷用(yòng)的Ⅰ類瓷、Ⅱ類瓷或Ⅲ類瓷的粉末按實際所需的配方進行配料、球磨、等靜壓成型、燒結、切片,制成電(diàn)容陶瓷基材;

②采用(yòng)200目絲網在電(diàn)容陶瓷基材一表面印刷銀漿;

③采用(yòng)網帶燒結爐進行高溫燒結,高溫燒結的溫度為(wèi)850℃,燒結頻率為(wèi)25±5Hz,燒結保溫時間為(wèi)15分(fēn)鍾;印刷銀層的厚度為(wèi)5~7微米。

二、在電(diàn)容陶瓷基材的另一表面上依次濺射钛鎢層、銅層和金層,具(jù)體(tǐ)包括以下步驟:

①一次清洗

使用(yòng)清洗液處理(lǐ)電(diàn)容陶瓷基材後使用(yòng)超聲波機清洗,清洗時間為(wèi)5±1分(fēn)鍾;然後烘幹,烘幹溫度為(wèi)100±5℃,烘幹時間為(wèi)30±5分(fēn)鍾。

②二次清洗

将一次清洗得到的電(diàn)容陶瓷基材放到等離子清洗機中(zhōng)進行二次清洗,清洗時間為(wèi)5±1分(fēn)鍾,烘幹溫度為(wèi)100±5℃,烘幹時間為(wèi)30±5分(fēn)鍾,同時活化表面。

③濺射钛鎢層

先将真空濺射鍍膜機抽真空到工(gōng)藝範圍,再充入氩氣作(zuò)為(wèi)工(gōng)作(zuò)氣體(tǐ),以钛與鎢的質(zhì)量比為(wèi)1:9的钛鎢合金作(zuò)為(wèi)靶材,在電(diàn)場作(zuò)用(yòng)下,Ar+加速轟擊靶材,将靶材原子濺射到電(diàn)容陶瓷基材上,在電(diàn)容陶瓷基材中(zhōng)沒有(yǒu)印刷銀層的表面上濺射一層钛鎢層,濺射厚度為(wèi)0.1~0.15微米。

④濺射銅層

先将真空濺射鍍膜機抽真空到工(gōng)藝範圍,再充入氩氣作(zuò)為(wèi)工(gōng)作(zuò)氣體(tǐ),以銅作(zuò)為(wèi)靶材,在電(diàn)場作(zuò)用(yòng)下,Ar+加速轟擊靶材,将靶材原子濺射到電(diàn)容陶瓷基材上,在钛鎢層表面上濺射一層銅層,濺射厚度為(wèi)0.1~0.2微米。

⑤濺射金層

先将真空濺射鍍膜機抽真空到工(gōng)藝範圍,再充入氩氣作(zuò)為(wèi)工(gōng)作(zuò)氣體(tǐ),以金作(zuò)為(wèi)靶材,在電(diàn)場作(zuò)用(yòng)下,Ar+加速轟擊靶材,将靶材原子濺射到電(diàn)容陶瓷基材上,在銅層表面上濺射一層金層,濺射厚度為(wèi)0.25~0.55微米。

三、根據所需單層芯片電(diàn)容的電(diàn)容值計算出單個芯片電(diàn)容的尺寸大小(xiǎo),然後利用(yòng)半導體(tǐ)砂輪劃片機對電(diàn)容陶瓷基材進行劃切,得到單個的單層芯片電(diàn)容。

四、測試分(fēn)選

使用(yòng)LCR電(diàn)橋測試儀對批量生産(chǎn)得到的單層芯片電(diàn)容逐個進行容量測試,将不符合容量要求範圍的産(chǎn)品分(fēn)選出來進行降級處理(lǐ)。

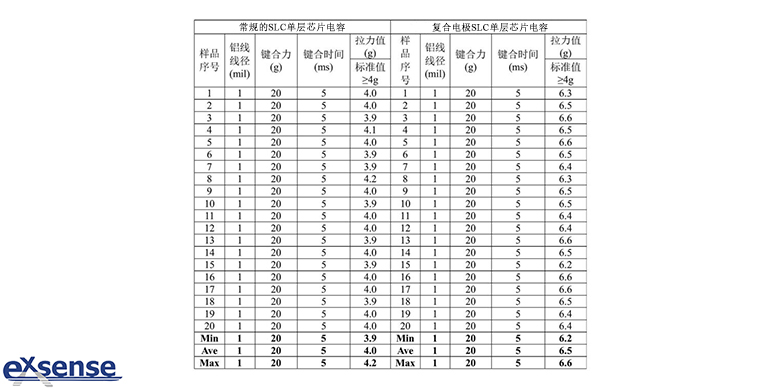

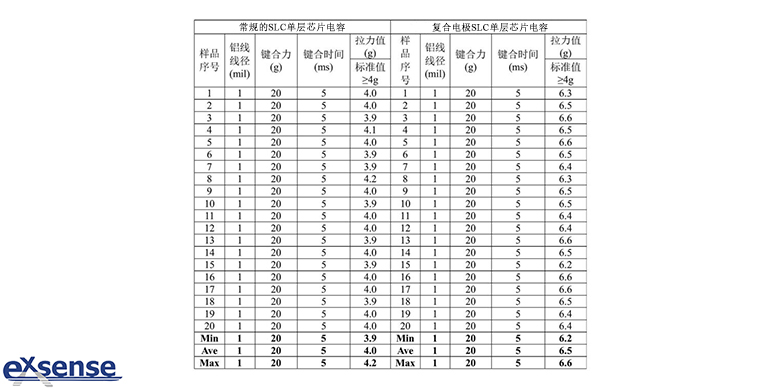

将常規的SLC單層芯片電(diàn)容與複合電(diàn)極SLC單層芯片電(diàn)容進行邦定(鍵合)對比試驗,試驗樣品的尺寸為(wèi)1.15*1.15*0.50mm,其電(diàn)容C=200pF±10%,損耗(DF):<100*10-4,絕緣(IR):>10*1010歐姆。通過錫膏回流焊将芯片電(diàn)容樣品焊接在電(diàn)路闆上之後,用(yòng)線(xiàn)徑1mil的鋁線(xiàn)與芯片電(diàn)容樣品的表面電(diàn)極鍵合,鍵合力為(wèi)20g,鍵合時間為(wèi)5ms,鍵合後利用(yòng)鍵合強度測試儀測試鍵合拉力,單位為(wèi)g。邦定(鍵合)對比試驗結果如下表:

由于钛鎢層、銅層和金層層疊而成的下表面電(diàn)極有(yǒu)效地解決了錫膏回流焊所産(chǎn)生的錫銀合金現象和銀遷移現象,因此複合電(diàn)極SLC單層芯片電(diàn)容與電(diàn)路闆能(néng)更好地焊接結合,不會存在因芯片電(diàn)容的銀遷移現象而造成芯片電(diàn)容與電(diàn)路闆分(fēn)離和松動的現象。因此,複合電(diàn)極SLC單層芯片電(diàn)容與鋁線(xiàn)鍵合強度更高,鍵合拉力大于标準值4g,最高可(kě)達6.6g,其邦定性能(néng)也明顯優于常規的SLC單層芯片電(diàn)容。

參考數據:

CN109659134A《一種高可(kě)靠雙面異質(zhì)複合電(diàn)極芯片電(diàn)容》