廣東愛晟電(diàn)子科(kē)技(jì )有(yǒu)限公(gōng)司生産(chǎn)的單層芯片電(diàn)容具(jù)有(yǒu)體(tǐ)積小(xiǎo)、結構堅固、頻率特性優異等特點,被廣泛應用(yòng)于微波通訊線(xiàn)路及抗電(diàn)磁幹擾(EMI,Electro Magnetic Interference)器件。與多(duō)層陶瓷電(diàn)容(MLCC)相比,單層芯片電(diàn)容具(jù)有(yǒu)等效串聯電(diàn)阻低、介質(zhì)損耗小(xiǎo)和可(kě)靠性高的優點。

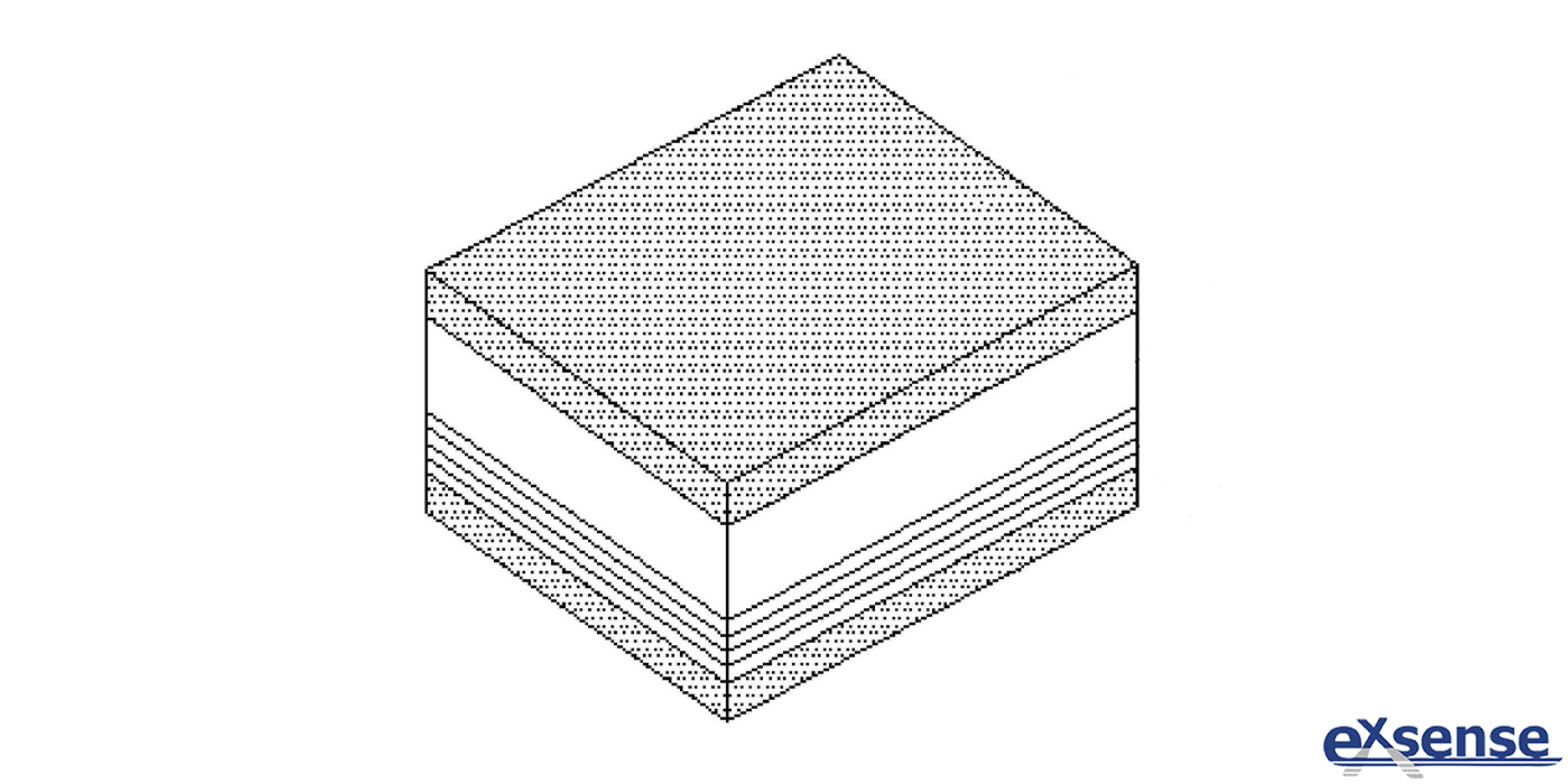

單層芯片電(diàn)容的基本結構為(wèi)金屬電(diàn)極——陶瓷介質(zhì)基片——金屬電(diàn)極的三層結構,其常規的制備工(gōng)藝流程為(wèi):流延→疊片→層壓切塊→排膠→燒結→濺射→電(diàn)鍍→切割。其中(zhōng),切割一般采用(yòng)機械切割方式,如旋轉刀(dāo)片切割。然而,陶瓷材料脆性大,刀(dāo)片切割時容易使陶瓷基片的切割面産(chǎn)生碎裂,不利于電(diàn)容器的結構完整性和可(kě)靠性。基于此,愛晟電(diàn)子為(wèi)大家介紹一款低應力單層芯片電(diàn)容,其陶瓷基片的切割面不易發生碎裂,具(jù)有(yǒu)結構完整性好和可(kě)靠性高的特點。

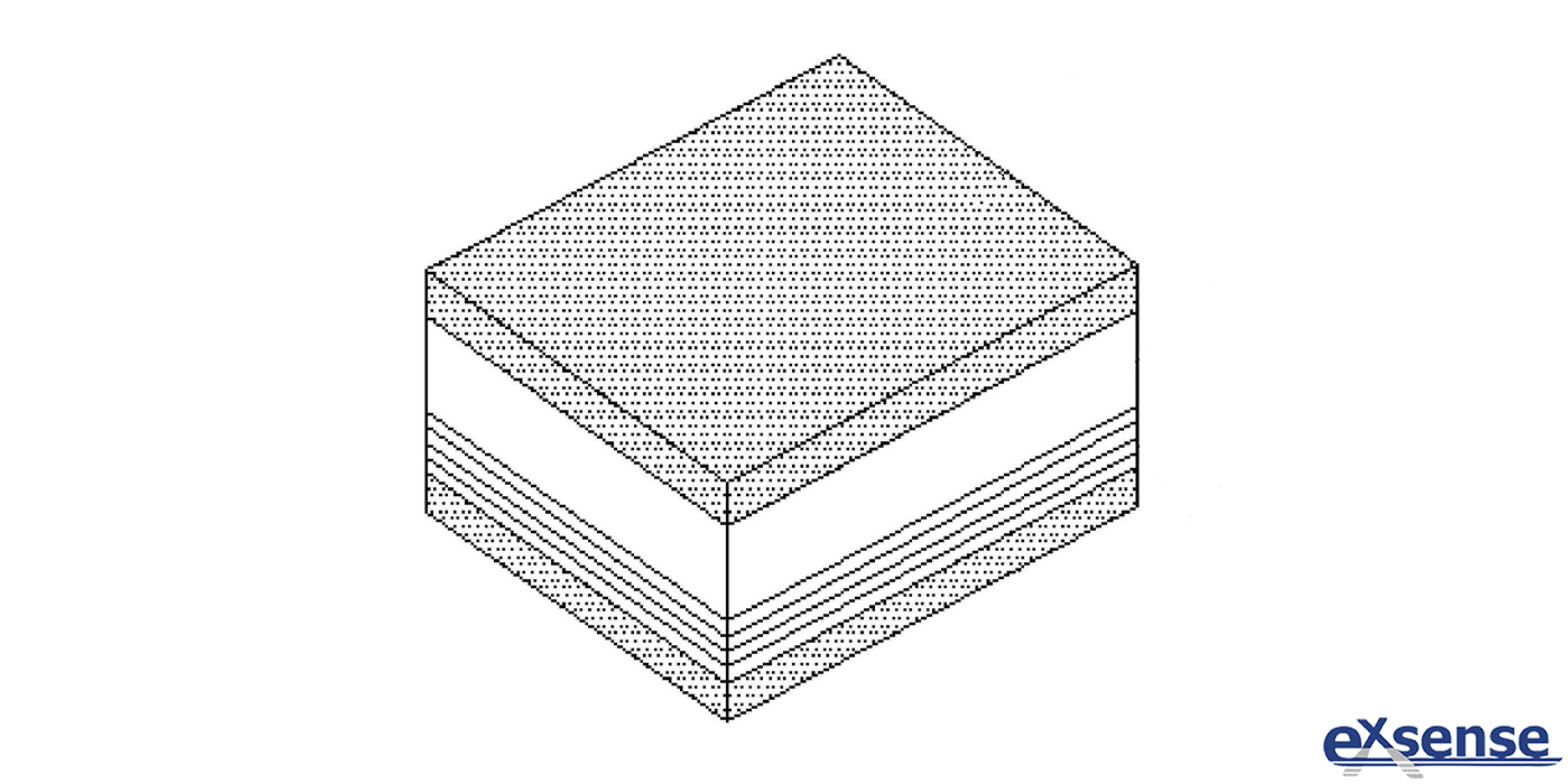

低應力單層芯片電(diàn)容包括陶瓷基片、面電(diàn)極、底電(diàn)極以及設于陶瓷基片内部的至少一個緩沖層。面電(diàn)極被設置于陶瓷基片的頂面;底電(diàn)極被設置于陶瓷基片的底面;各緩沖層在垂直于陶瓷基片的底面的方向上間隔設置,緩沖層為(wèi)内部中(zhōng)空的呈封閉框形的金屬層,其邊框沿陶瓷基片的側面布置,并外露于陶瓷基片的側面。緩沖層能(néng)減少切割應力對陶瓷基片的切割面的影響,避免切割面産(chǎn)生碎裂,從而使單層芯片電(diàn)容整體(tǐ)結構完好,保證單層芯片電(diàn)容的性能(néng)和可(kě)靠性。同時,通過設置至少一個間隔設置的金屬層,能(néng)夠分(fēn)散切割應力,防碎裂效果更好。低應力單層芯片電(diàn)容的制備方法如下:

一、采用(yòng)流延法将陶瓷漿料制成陶瓷膜。

陶瓷漿料可(kě)采用(yòng)本行業所慣用(yòng)的工(gōng)藝技(jì )術用(yòng)陶瓷粉料制備得到,陶瓷粉料可(kě)采用(yòng)電(diàn)容陶瓷用(yòng)的Ⅰ類瓷、Ⅱ類瓷或Ⅲ類瓷的粉末配成;制得陶瓷膜的厚度為(wèi)5~60微米。

二、采用(yòng)金屬漿料在步驟一制得的陶瓷膜表面印刷呈多(duō)個封閉框形的緩沖層。

金屬漿料可(kě)以為(wèi)銀、钯、銀钯合金、鎳、銅、鎳銅合金等的漿料,優先選用(yòng)可(kě)與步驟一制得的陶瓷膜共燒的金屬漿料。采用(yòng)絲網印刷法印刷緩沖層,得到的緩沖層呈縱橫交錯的方格網狀,印刷緩沖層的厚度為(wèi)0.5~3微米。

三、将步驟一制得的陶瓷膜與至少一個步驟二中(zhōng)得到的陶瓷膜進行疊片、層壓,得到各緩沖層間隔設于底部的陶瓷生坯巴塊。

疊片為(wèi)先将四個步驟二得到的陶瓷膜層疊在一起,并使四個陶瓷膜上的緩沖層相互間隔,然後在外露的緩沖層的一側再層疊多(duō)個步驟一制得的陶瓷膜直至達到芯片電(diàn)容所需的厚度;所得陶瓷生坯巴塊中(zhōng)相鄰兩個緩沖層的間距相等且為(wèi)5~ 20微米。

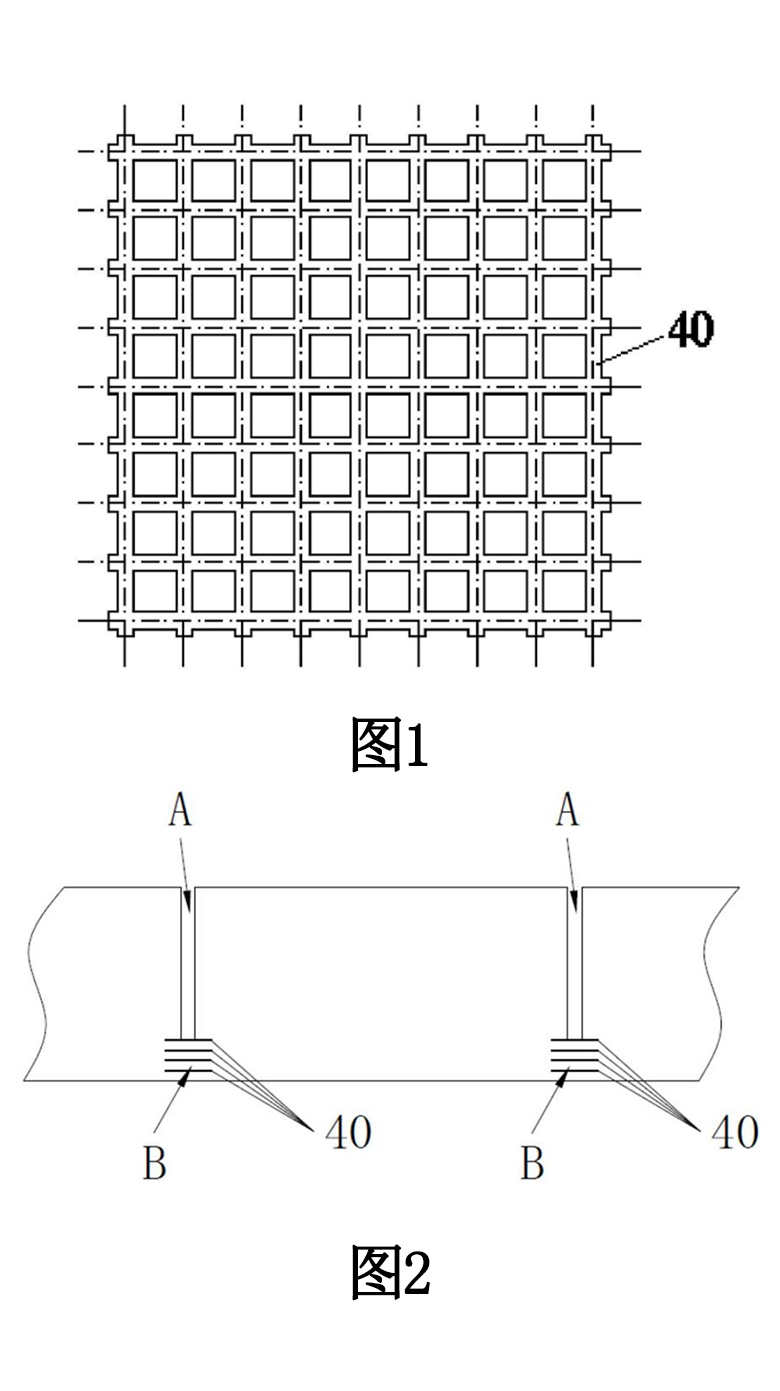

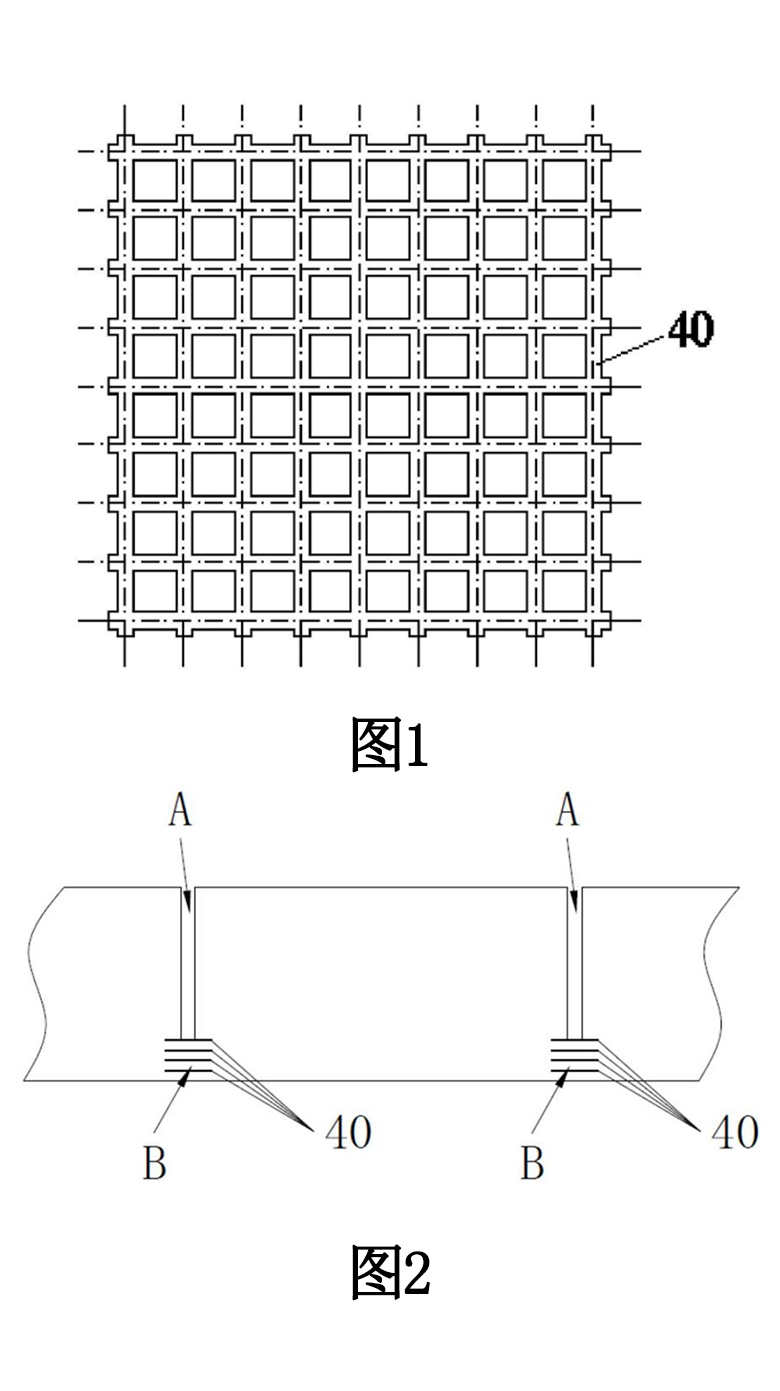

四、将步驟三得到的陶瓷生坯巴塊劃切成尺寸更小(xiǎo)的陶瓷生坯小(xiǎo)塊,然後從上至 下沿緩沖層的邊框中(zhōng)線(xiàn)對陶瓷生坯小(xiǎo)塊預切割成槽,如圖1所示,圖中(zhōng)點劃線(xiàn)為(wèi)切割線(xiàn),且所得切槽A底部為(wèi)含緩沖層40的預留部分(fēn)B,該預留部分(fēn)B不切斷,如圖2所示。

劃切得到的陶瓷生坯小(xiǎo)塊為(wèi)矩形,其長(cháng)和寬分(fēn)别優選為(wèi)2~10毫米,陶瓷生坯小(xiǎo)塊面積較小(xiǎo),操作(zuò)起來比較方便,不容易折斷,并且燒結時不容易變形,保證燒結後的平整度好;切槽A的深度為(wèi)陶瓷生坯小(xiǎo)塊的厚度的2/3~4/5,則預留部B的厚度為(wèi)陶瓷生坯小(xiǎo)塊的厚度的1/5~1/3;劃切和預切割可(kě)以采用(yòng)旋轉刀(dāo)片切割。

五、将步驟四得到的半成品進行排膠、燒結。

排膠是将步驟四得到的半成品在空氣中(zhōng)以250~400℃進行排膠,以保證燒結後的陶瓷均勻緻密。燒結是将排膠後的半成品在空氣中(zhōng)或還原氣氛中(zhōng)以900~1350℃進行燒結。

六、在步驟五得到的半成品的頂面和底面分(fēn)别制作(zuò)面電(diàn)極和底電(diàn)極。

采用(yòng)濺射或電(diàn)鍍方式制作(zuò)面電(diàn)極和底電(diàn)極,材料可(kě)為(wèi)钛、鎢、鉑、钴、銅、 鎳、钯、金、錫中(zhōng)的至少一種金屬或任意幾種組合而成的合金,制得的面電(diàn)極與底電(diàn)極的厚度分(fēn)别為(wèi)2微米。

七、沿切槽對步驟六得到的半成品進行貫穿式切割,切斷預留部B,得到單個低應力單層芯片電(diàn)容。

低應力單層芯片電(diàn)容的制備方法中(zhōng),根據步驟一流延法得到的陶瓷膜面積較大,不方便後續的處理(lǐ)。因此,在步驟四中(zhōng),利用(yòng)陶瓷生坯可(kě)塑性的特點,先将陶瓷生坯巴塊劃切成較小(xiǎo)的陶瓷生坯小(xiǎo)塊,并對得到的陶瓷生坯小(xiǎo)塊預切割成槽,所以層壓後對其劃切和預切割就不會産(chǎn)生碎裂。完成步驟五和步驟六後,在步驟七中(zhōng)再切斷預留部,雖然此時切割對象為(wèi)脆性較大的陶瓷熟料,但由于預留部分(fēn)含有(yǒu)可(kě)緩沖切割應力的緩沖層,因此切斷時能(néng)防止碎裂,而且相對于現有(yǒu)技(jì )術,對陶瓷熟料的切割厚度大為(wèi)減少,更有(yǒu)效防止切割面發生碎裂。